Двухтактные триггеры

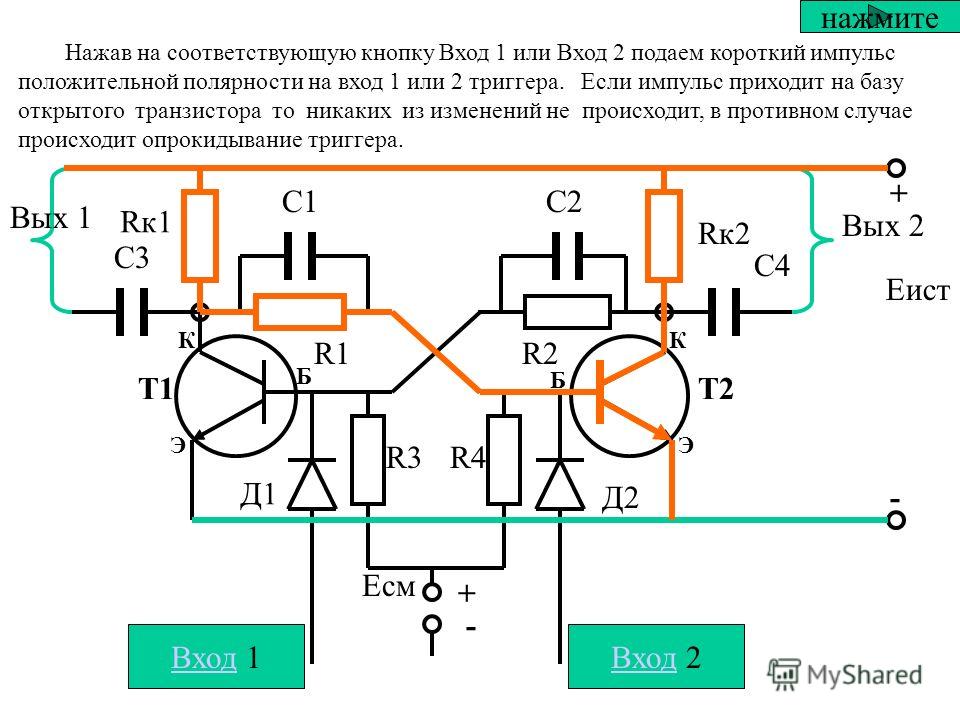

К основным недостаткам рассмотренных выше однотактных триггеров следует отнести: срабатывание триггеров по уровню импульса, в результате чего за время тактового импульса, при изменении уровня на информационных входах, триггер меняет свое состояние; наличие аналоговых элементов задержки сильно усложняет схему и накладывает ограничение на её работу (τи < τз в T-триггере).

Исключить эти недостатки позволяют двухтактные триггеры, в которых запоминание информации осуществляется по фронту тактового импульса.

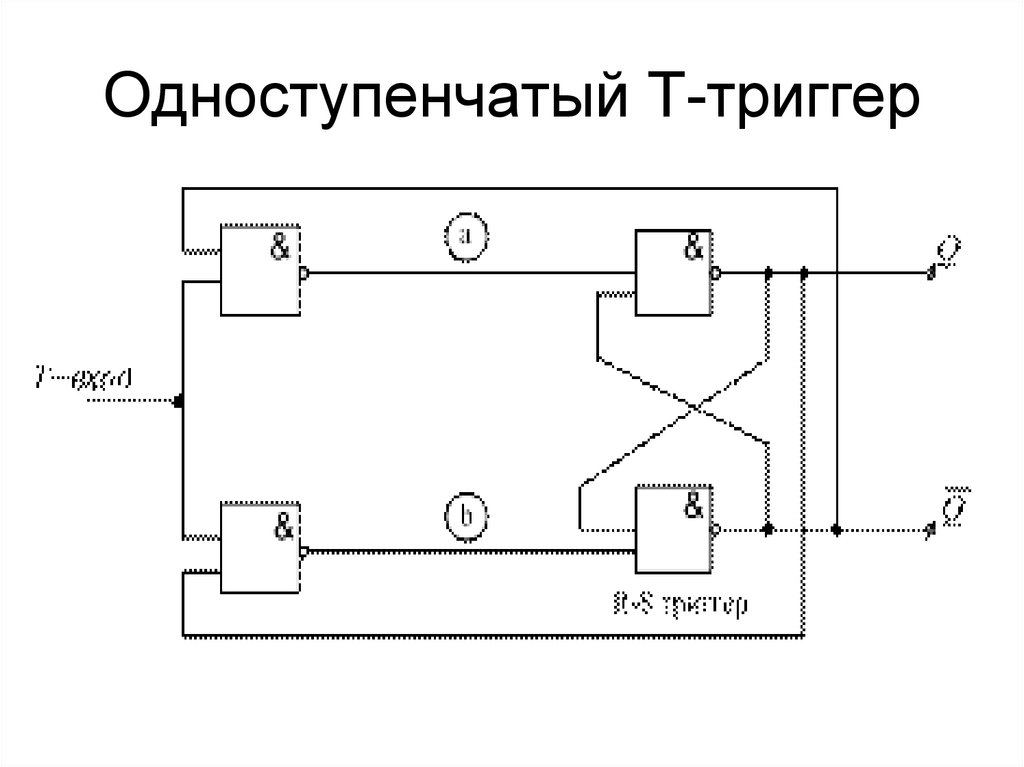

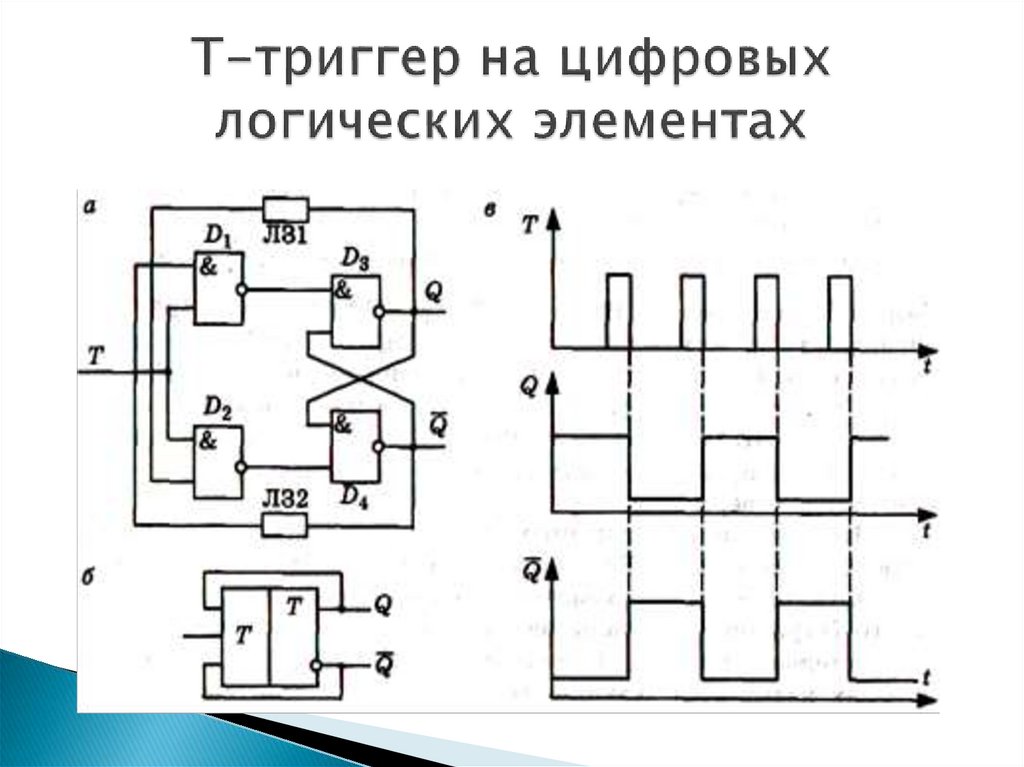

Триггер T-типа. Двухтактные триггеры Т-типа выполняются на базе двух однотактных RS-триггеров, один из которых называют основным (DD2), а другой – вспомогательным (DD1). Особенностью рассматриваемой схемы является наличие в ней дополнительного инвертора (DD3), управляющего вспомогательным триггером DD1.

Рис. | |

Пусть в начальный момент триггер DD2 находится в состоянии 0, (рис. 3.35). Тогда через обратные связи на вход R вспомогательного триггера DD1 действует лог.1, а на вход S – лог.0. Как только на тактовый сигнал T подается лог.1, триггер DD1 сбрасывается (). На вход R основного триггера DD2 начинает действовать лог.0, а на вход S – лог.1. Установка сигнала T в низкое состояние приведет к тому, что через инвертор DD3 на тактовый вход основного триггера DD2 будет действовать лог.1. Это приведет к записи в DD2 лог.1, т.е. триггер переключится в противоположное состояние. Таким образом, каждый задний фронт тактового импульса будет приводить к переключению триггера.

Двухтактный

триггер D-типа. Двухтактные

триггеры D-типа выполняются на базе двух

однотактных D-триггеров, один из которых

называют основным, а другой –

вспомогательным (рис. 3.36). В них

последовательно записывается информация

по двум тактовым импульсам – T1 и T2 .

Пунктиром показана электрическая связь для организации двухтактного счетного триггера.

а) б)

Рис. 3.41. Двухтактный D-триггер (а) и его временные диаграммы (б)

Двухтактные

триггеры могут работать: по

переднему фронту или по заднему фронту.

Тактовые входы таких триггеров на УГО

обозначаются косой чертой (рис. 3.37).

3.37).

Рис. 3.42. D-триггер, срабатывающий по переднему (слева) и по заднему (справа) фронту тактового импульса

Регистрами называются многоразрядные цифровые запоминающие устройства, предназначенные для приёма, хранения, преобразования и передачи информации.

Основу регистра составляют триггеры. Обычно используются D-триггеры, как наиболее удобные для записи и хранения информации. Чаще всего используются двухтактные D-триггеры, в которые запоминание осуществляется по фронту тактового импульса, гораздо реже – RS-триггеры.

Регистры делятся на параллельные, последовательные и параллельно-последовательные.

Рис. 3.43. Параллельный регистр |

Параллельные регистры. Параллельный n-разрядный

регистр представляет собой n триггеров, на информационные входы

которых подается n-разрядный

двоичный код, который необходимо

запомнить, а на объединенные тактовые C-входы

подаётся тактовый импульс, по переднему

фронту которого осуществляется

запоминание (рис. 3.38). В регистре может

быть дополнительный вход R сброса

регистра в нулевое состояние.

Параллельный n-разрядный

регистр представляет собой n триггеров, на информационные входы

которых подается n-разрядный

двоичный код, который необходимо

запомнить, а на объединенные тактовые C-входы

подаётся тактовый импульс, по переднему

фронту которого осуществляется

запоминание (рис. 3.38). В регистре может

быть дополнительный вход R сброса

регистра в нулевое состояние.

Последовательные регистры. Последовательные регистры работают с последовательным кодом, разряды которого разделены во времени на интервалы, равные периоду следования тактового импульса T. Такой способ представления информации широко используется при передаче информации между цифровыми устройствами, что позволяет экономить количество проводов, по которым передаётся информация. Недостатком является значительное время передачи информации.

Различают регистры прямого

сдвига и реверсивные

регистры. Регистры

прямого сдвига осуществляют приём

(передачу) информации, сдвигая её в

регистре на 1 разряд вправо при приходе

одного тактового импульса. Для полного

приёма (передачи) информации требуется n тактов. Регистр представляет собой n последовательно соединённых D-триггеров,

тактовые входы которых объединены.

Имеется один информационный вход I для приёма информации (рис. 3.39). Вход

R позволять сбросить все триггеры

регистра одновременно.

Для полного

приёма (передачи) информации требуется n тактов. Регистр представляет собой n последовательно соединённых D-триггеров,

тактовые входы которых объединены.

Имеется один информационный вход I для приёма информации (рис. 3.39). Вход

R позволять сбросить все триггеры

регистра одновременно.

Реверсивный сдвиговый регистр позволяет осуществить сдвиг информации внутри регистра как вправо, так и влево. Это может потребоваться для преобразования последующего кода. Например, если первоначально следовал старший разряд кода, то после преобразования первым будет преобразован младший разряд кода. Для организации реверсивного режима между входами и выходами триггеров включаются одноразрядные мультиплексоры с двумя информационными входами (рис. 3.40).

Рис. 3.44. Последовательный регистр прямого сдвига

Рис. 3.45. Реверсивный регистр

Вход

V управляет направлением сдвига

информации. При V = 0 к выходу мультиплексора

подключён вход I1 и схема преобразуется

в схему со сдвигом информации вправо.

При V = 1 к входам мультиплексора подключён

вход I2. При этом выход последующего

триггера подключается к информационному

входу предыдущего, и таким образом при

приходе тактовых импульсов осуществляется

сдвиг информации влево.

При V = 0 к выходу мультиплексора

подключён вход I1 и схема преобразуется

в схему со сдвигом информации вправо.

При V = 1 к входам мультиплексора подключён

вход I2. При этом выход последующего

триггера подключается к информационному

входу предыдущего, и таким образом при

приходе тактовых импульсов осуществляется

сдвиг информации влево.

Параллельно-последовательные регистры. Такие регистры служат для преобразования информации с последовательного кода в параллельный или наоборот, а также могут выполнять функции как последовательных, так и параллельных регистров.

Для организации одновременного наличия двух режимов (параллельного и последовательного) чаще пользуются более простым схемотехническим решением – между триггерами включают одноразрядный мультиплексор (рис. 3.41).

Рис. 3.46. Параллельно-последовательный регистр

При

V = 0 организуется режим параллельного

регистра. При этом в мультиплексорах к

выходам подключены входы I1, на которые

подаётся параллельный код.

Рис. 3.47. Параллельно-последовательный реверсивный регистр

Память

Запоминающие

устройства (ЗУ) или память предназначены для запоминания некоторого

количества многоразрядных чисел и

представляют собой такое же количество

линейных регистров. Выбор линейного

регистра осуществляется с помощью

дешифратора, который обычно встроен в

микросхему. Использование встроенных

дешифраторов позволяет значительно

сократить количество выводов микросхемы,

так как для входов и выходов регистра

используются одни и те же выводы

микросхемы, подключаемые к разным

регистрам через цифровые ключи,

управляемые от дешифратора.

Рис. 3.48. Структурная схема запоминающего устройства:

m – количество разрядов каждого числа; n – разрядность адресного кода

Оперативное запоминающее устройство (ОЗУ). ОЗУ используются для многократной перезаписи в них информации. ОЗУ бывают статические и динамические. Статические строятся на основе триггеров, а в динамических в качестве запоминающих элементов (ЗЭ) используются ёмкости (конденсаторы), подключённые через полевой транзистор к шине данных, чтобы увеличить время разряда.

Рис. 3.49. Фрагмент структурной схемы динамического ОЗУ |

Достоинством динамических

ОЗУ является значительное сокращение

транзисторов, используемых для построения

запоминающих элементов. Недостатком

динамических ОЗУ является наличие

ёмкости, которая имеет свойства

разряжаться с течением времени. Этот

недостаток устраняется путём организации

режима регенерации, т.е. восстановления

напряжения на ёмкости через заданный

интервал времени – обычно от 1 до 10 мкс.

Недостатком

динамических ОЗУ является наличие

ёмкости, которая имеет свойства

разряжаться с течением времени. Этот

недостаток устраняется путём организации

режима регенерации, т.е. восстановления

напряжения на ёмкости через заданный

интервал времени – обычно от 1 до 10 мкс.

На рисунке 3.44, кроме ЗЭ, упрощенно показаны цепи, необходимые для пояснения принципов записи-считывания информации. Запоминающий элемент включает конденсатор СП и транзисторный ключ VT1, подключающий этот конденсатор к шине данных (ШД). Затвор транзистора VT1 подключен к выходу дешифратора адреса CS. Поэтому при появлении на данном выходе дешифратора напряжения высокого уровня транзистор VT1 открывается, подключая конденсатор СП к ШД. В этом случае в зависимости от режима работы можно либо считать информацию, либо записать новую.

К

ШД

подключен затвор транзистора VT2,

выполняющего роль усилителя считывания.

После подключения нужного конденсатора

к ШД

с выхода усилителя снимается напряжение,

пропорциональное исходному напряжению

на конденсаторе СП. ШД

имеет большую собственную емкость СШ.

Как правило, выполняется условие СШ > СП.

Подключение к ШД

конденсатора малой емкости за счет

перераспределения зарядов емкостей СШ и СП незначительно изменяет ее потенциал.

Для распознания этого изменения

необходимо очень точно знать исходное

напряжение шины, которое в процессе

работы может принимать произвольное

значение. Поэтому процесс считывания

информации предполагает следующую

последовательность действий:

ШД

имеет большую собственную емкость СШ.

Как правило, выполняется условие СШ > СП.

Подключение к ШД

конденсатора малой емкости за счет

перераспределения зарядов емкостей СШ и СП незначительно изменяет ее потенциал.

Для распознания этого изменения

необходимо очень точно знать исходное

напряжение шины, которое в процессе

работы может принимать произвольное

значение. Поэтому процесс считывания

информации предполагает следующую

последовательность действий:

– непосредственно перед считыванием информации фиксируют уровень напряжения ШД, для чего при помощи ключа VT3 емкость СШ заряжают до напряжения питания;

– на нужный запоминающий элемент подают сигнал выборки CS; СП подключается к СШ, что сопровождается перераспределением заряда и соответствующим изменением напряжения на ШД;

–

с выхода усилителя считывают сигнал,

пропорциональный заряду конденсатора

выбранного запоминающего элемента.

Считывание информации сопровождается ее разрушением. Запись информации выполняется с использованием транзисторов VT3 и VT4, которые по сигналу управления подключают ШД либо к источнику питания, либо к общей шине. При выборке нужного запоминающего элемента его конденсатор заряжается до напряжения ШД.

Реальная структура ИС динамического ОЗУ много сложнее показанного упрощенного варианта. Она содержит регистры и цепи управления процессами регенерации, а также дополнительную матрицу запоминающих элементов, использующуюся в качестве эталона. Для регенерации по сигналу с блока управления содержимое целой строки матрицы переписывается в регистр и обратно, за счет чего поддерживается требуемый уровень напряжения на конденсаторах памяти.

Постоянные запоминающие

устройства (ПЗУ). ПЗУ

предназначены для длительного хранения

записанной в них информации без

перезаписи. Они

бывают масочные

(информация в них записывается

непосредственно в процессе их

изготовления), с однократным

программированием (обычно путём

прожигания информации) и с многократным

программированием (ультрафиолетовое

или электрическое стирание информации).

Особенностью ПЗУ является отсутствие входов записи информации (программирование или прожигание осуществляется через выходы регистра, а в качестве запоминающих элементов обычно используют диоды или транзисторы в режиме инвертирующего повторителя).

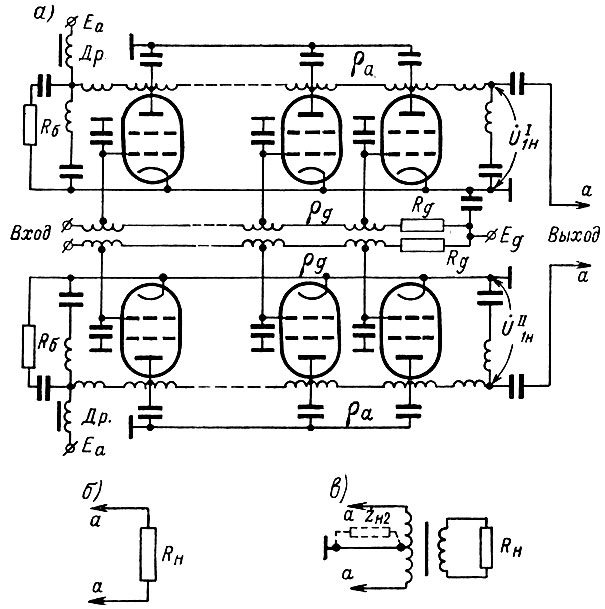

На рисунке 3.45 приведена схема простейшего ПЗУ с организацией 4×8. Она включает дешифратор с двумя адресными шинами, восемь балластных резисторов Rб1-Rб8 выходных шин и диоды, число которых равно числу логических 1, записанных в ПЗУ.

Рис. 3.50. ПЗУ с организацией 4×8

Работа

ПЗУ сводится к следующему. После появления

на выходе дешифратора напряжения

высокого уровня, при наличии связи через

диод между адресной шиной и шиной данных,

это напряжение прикладывается к

соответствующему балластному резистору,

что воспринимается как появление на

шине сигнала логической единицы. При

отсутствии связи ток через соответствующий

резистор не протекает, что классифицируется

как сигнал логического нуля.

а) б) |

Рис. 3.51. Фрагменты масочных ПЗУ на биполярных (а) и полевых (б) транзисторах |

В масочных ПЗУ связь между шиной дешифрованного адреса и шиной данных обеспечивается с помощью транзисторов, у которых могут отсутствовать некоторые части. Отсутствие части транзистора классифицируется как отсутствие связи (рис. 3.46).

В

ПЗУ с однократным программированием

первоначально имеется связь между шиной

дешифрованного адреса и шиной данных

для всех запоминающих элементов. Процесс

записи осуществляется путем разрушения

(пережигания) специально для этого

предусмотренных перемычек между шинами

дешифрированного адреса и выходными

выводами. Такие перемычки изготавливаются

из нихрома, поликремния или титаната

вольфрама и имеют собственное сопротивление

в несколько десятков Ом. Перемычка

обычно включается в эмиттерную цепь

транзистора. При программировании для

разрушения такой перемычки через

транзистор достаточно пропустить

импульс тока в 20…30 мА при длительности

порядка 1мс. В нормальном режиме работы

токи схемы существенно меньше необходимых

для программирования, поэтому записанная

информация при чтении не разрушается.

Перемычка

обычно включается в эмиттерную цепь

транзистора. При программировании для

разрушения такой перемычки через

транзистор достаточно пропустить

импульс тока в 20…30 мА при длительности

порядка 1мс. В нормальном режиме работы

токи схемы существенно меньше необходимых

для программирования, поэтому записанная

информация при чтении не разрушается.

Рис. 3.52. Запоминающий элемент репрограммируемого ПЗУ |

Репрограммируемые ПЗУ по сути являются электростатическими ЗУ. Логика построения их запоминающих элементов подобна логике запоминающих элементов динамического ОЗУ. Отличие состоит в том, что непосредственно носителем информации в них является не конденсатор, а специализированный МДП-транзистор (транзистор с «плавающим» затвором или МДП-транзистор с двухслойным диэлектриком) (рис. 3.47).

Транзистор

VT1 служит для выбора по сигналу с выхода

дешифратора адреса соответствующего

транзистора памяти – VT2. Шина через

ограничительный резистор подключена

к выводу источника питания. При отпирании

транзистора VT1 протекание тока в цепи

его стока зависит от состояния транзистора

VT2. Наличие или отсутствие тока

классифицируется как хранение сигналов

логический 0 или логическая 1. Обычно,

если ток в цепи стока VT2 протекает,

считают, что в ячейке был записан сигнал

логический 0, если ток отсутствует –

сигнал логическая 1.

Шина через

ограничительный резистор подключена

к выводу источника питания. При отпирании

транзистора VT1 протекание тока в цепи

его стока зависит от состояния транзистора

VT2. Наличие или отсутствие тока

классифицируется как хранение сигналов

логический 0 или логическая 1. Обычно,

если ток в цепи стока VT2 протекает,

считают, что в ячейке был записан сигнал

логический 0, если ток отсутствует –

сигнал логическая 1.

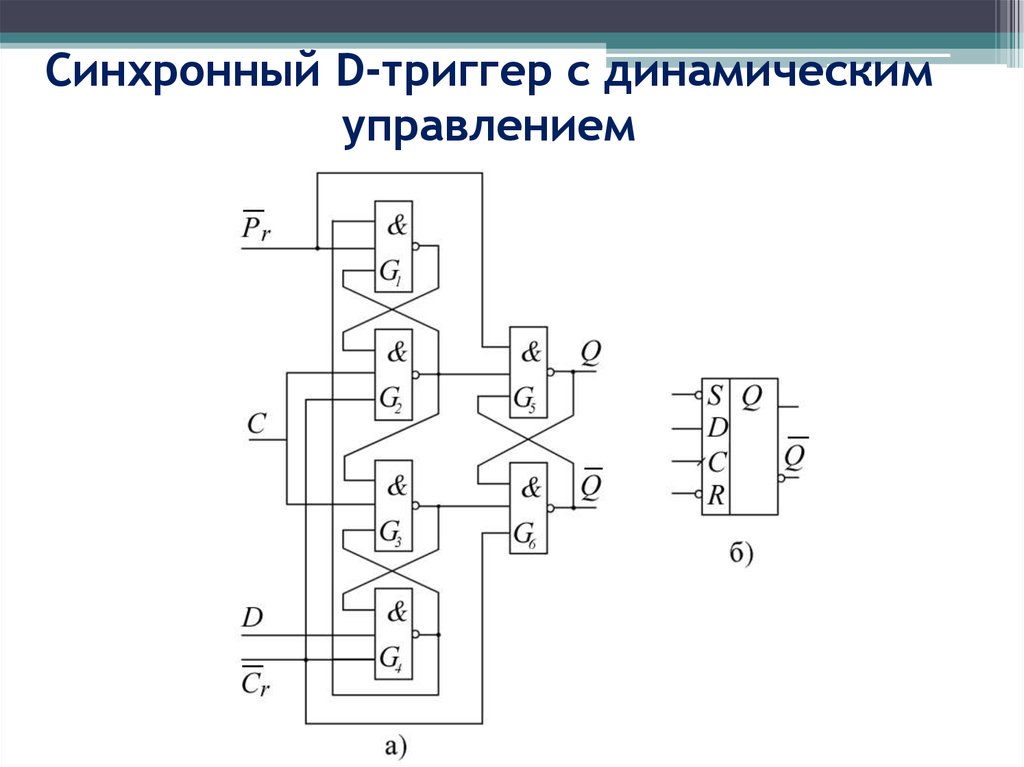

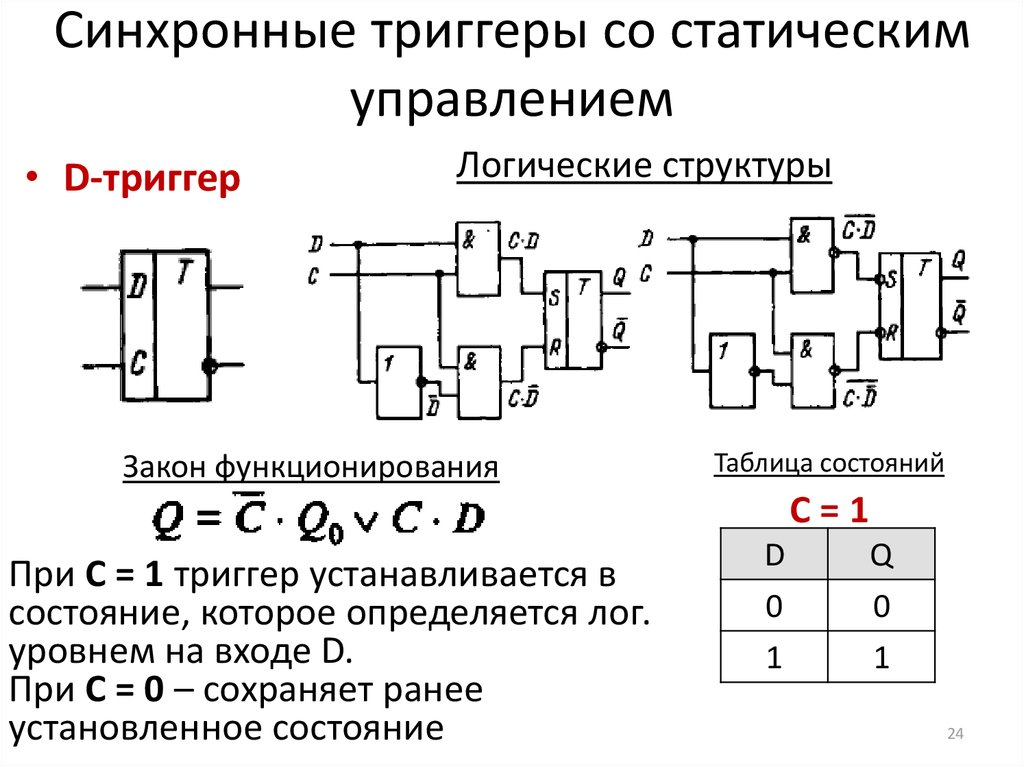

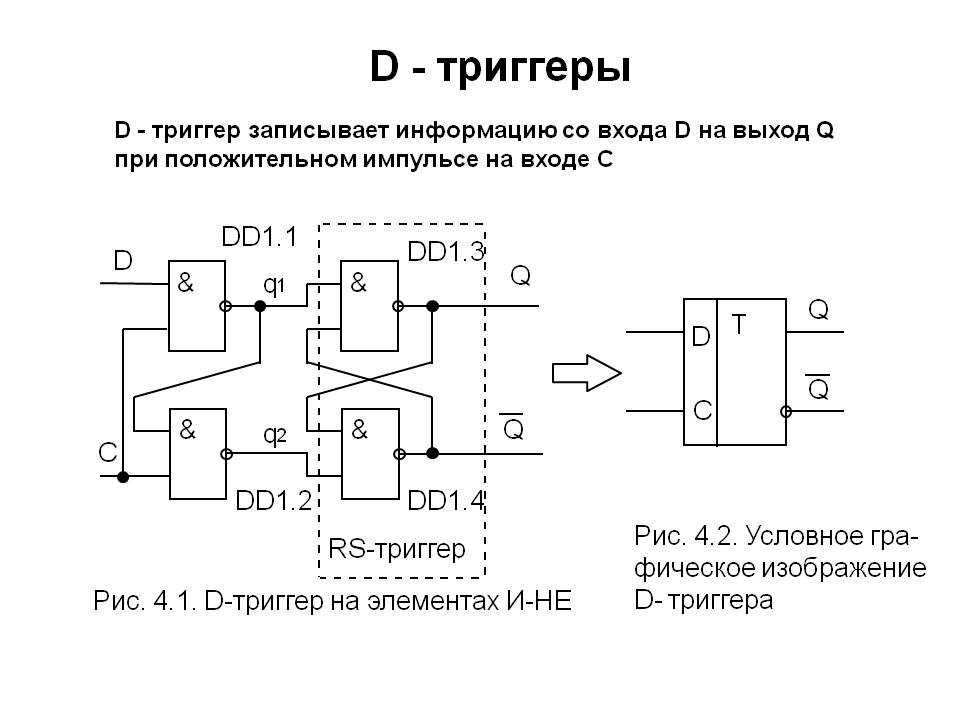

Двухтактный ( двухступенчатый) D-триггер

D — триггер можно выполнить двухступенчатым.

Первая ступень представляет собой одноступенчатый D-триггер, а вторая — синхронный RS-триггер.

На схемах двухтактный D- триггер обозначается следующим образом.

Рис. 0.21

Принцип действия двухтактного D- триггера основан на принципе действия RS триггера с динамическими входами. Т.е. первая ступень переключается по переднему фронту тактового импульса, вторая по его срезу.

Схема двухтактного D- триггера имеет следующий вид.

Рис. 0.22

Работа двухтактного D- триггера наглядно отражена в описании его принципа работы

Так же как и в одноступенчатом D-триггере в 2-х ступенчатой схеме возможно реализовать функцию valve. В результате получим универсальный 2-х ступенчатый DV-триггер.

Рис. 0.23

Условное обозначение такого триггера имеет следующий вид:

Рис. 0.24

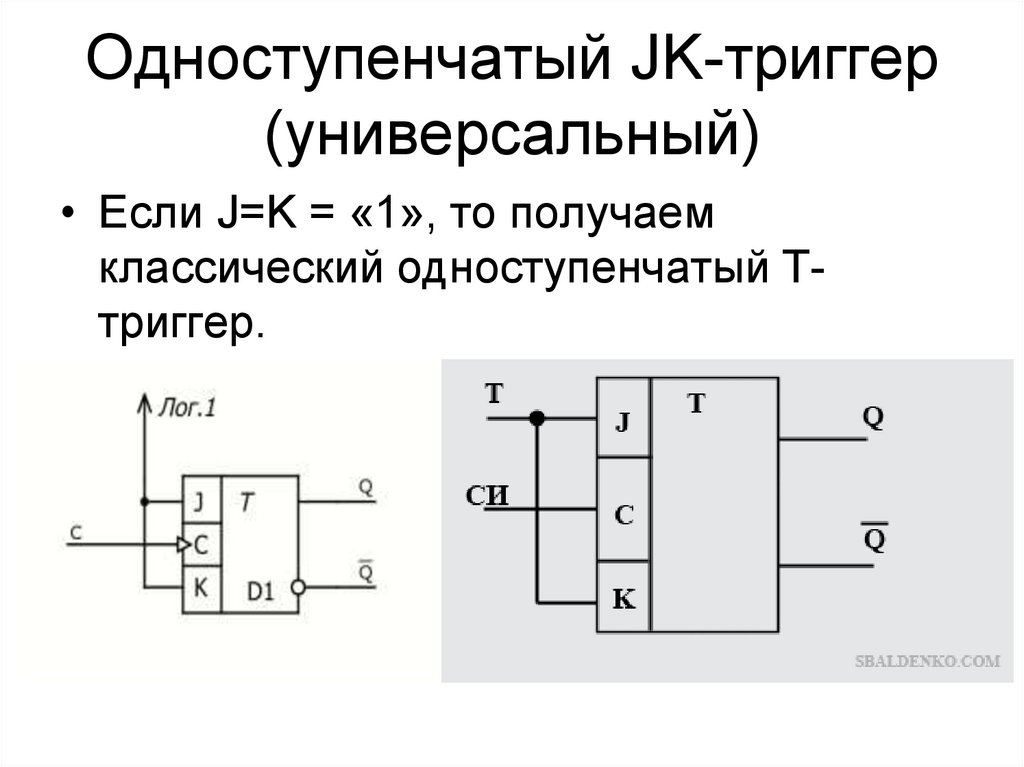

Двухступенчатый D-триггер получил широкое применение из-за его универсальности. Так, например, если соединить с D входом, то с каждым синхроимпульсом будет меняться потенциал на входе D и, следовательно, состояние триггера. Таким образом, получается счетный Т-триггер.

Рис. 0.25

Кроме того, на базе таких триггеров можно реализовать и другие виды триггеров.

Развитие универсальных триггеров происходит в связи с необходимостью экономии средств при проектировании и изготовлении радиоэлектронной аппаратуры.

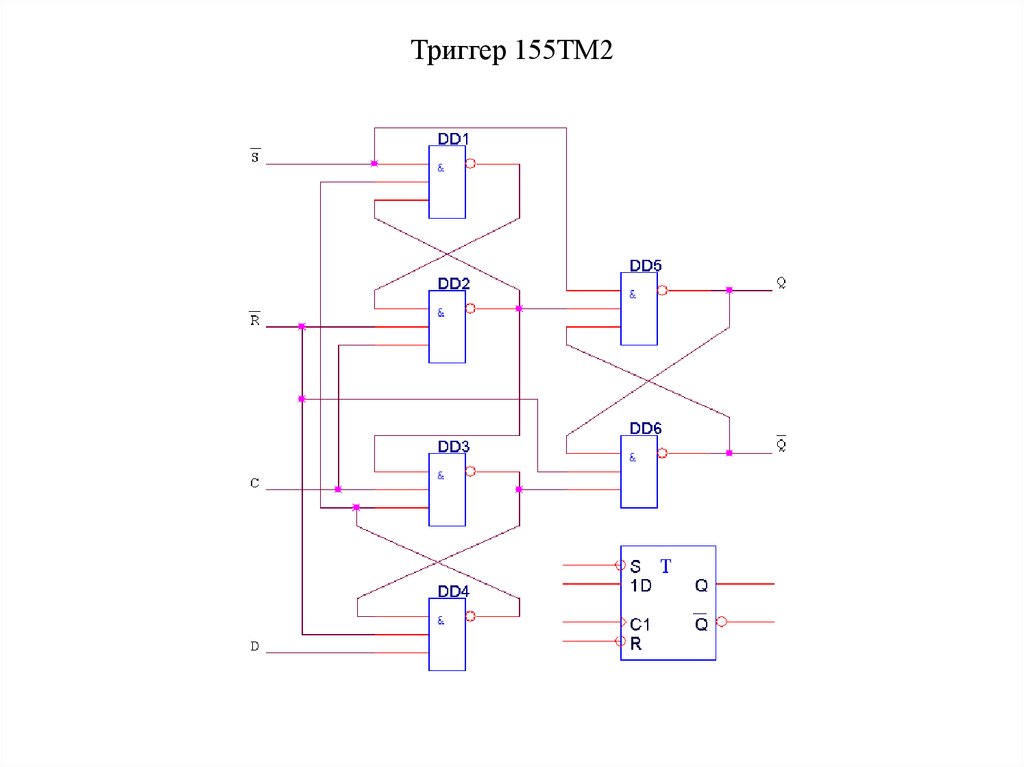

Реальные микросхемы функционально являющиеся D -триггерами обозначаются следующим образом: ТМ. Так, например, микросхема 155ТМ2 является D-триггером.

Итак D-триггеры, цифровые устройства со счётным запуском, и не имеющие запрещённых комбинаций сигналов, подаваемых на их информационные входы.

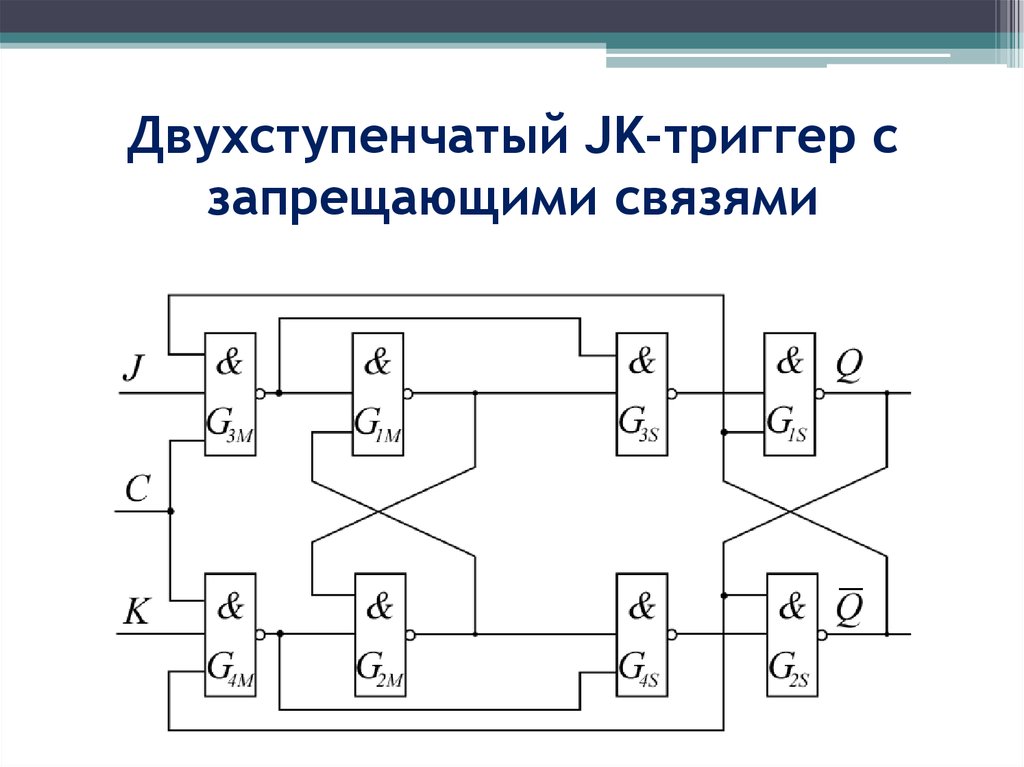

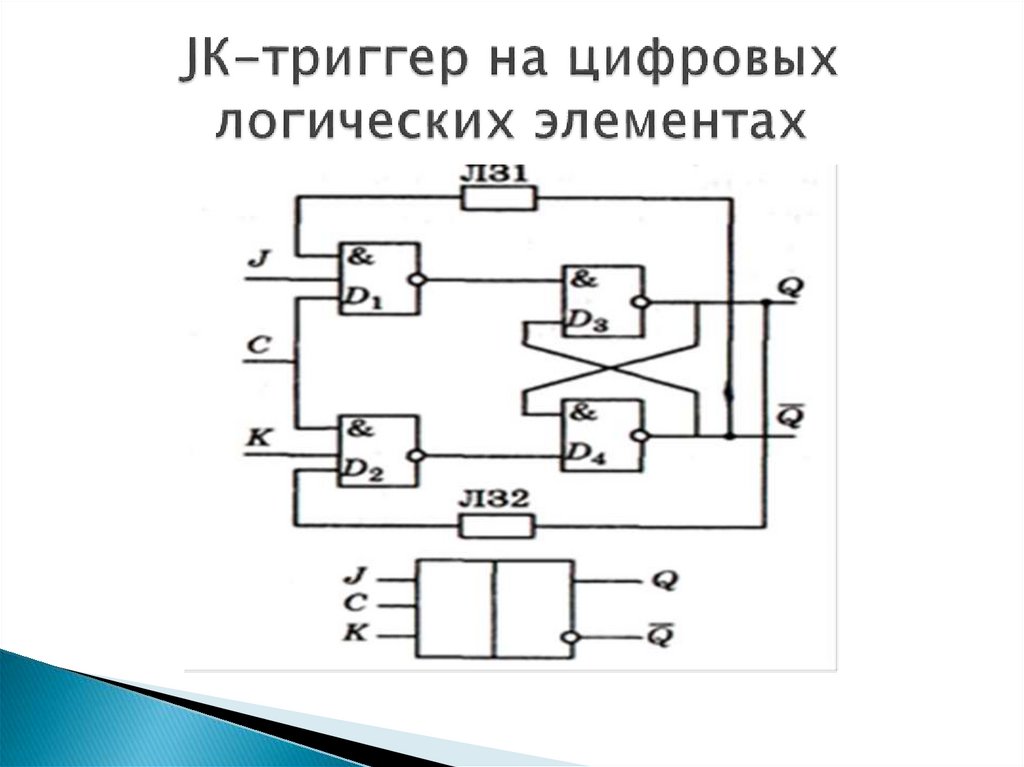

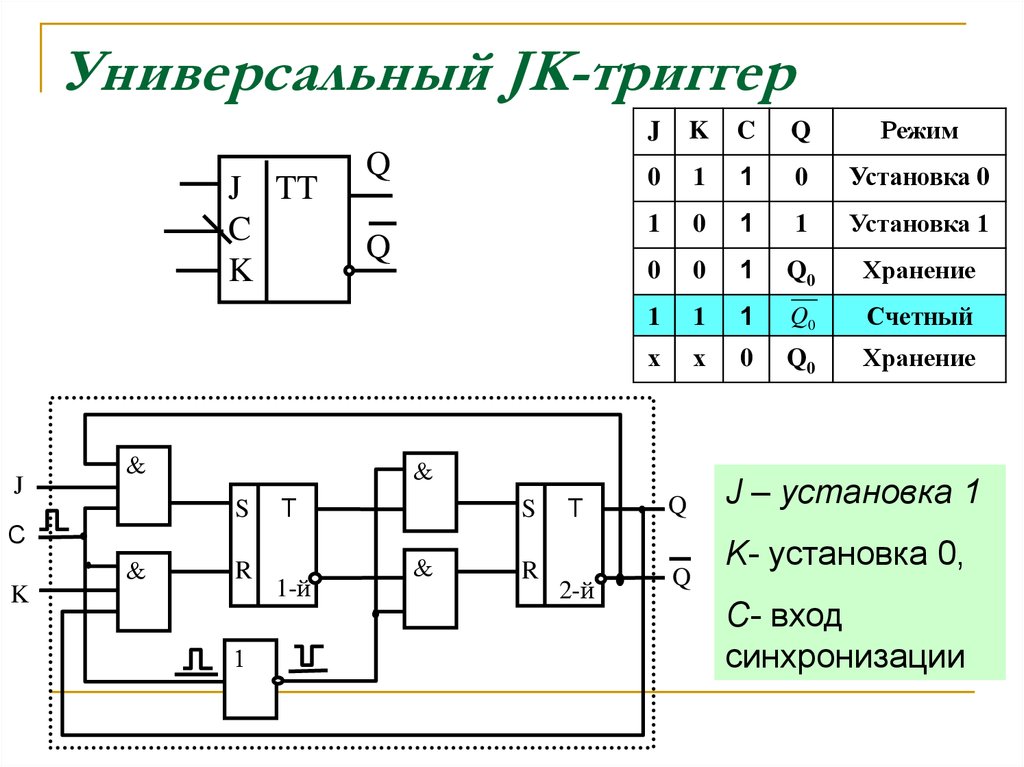

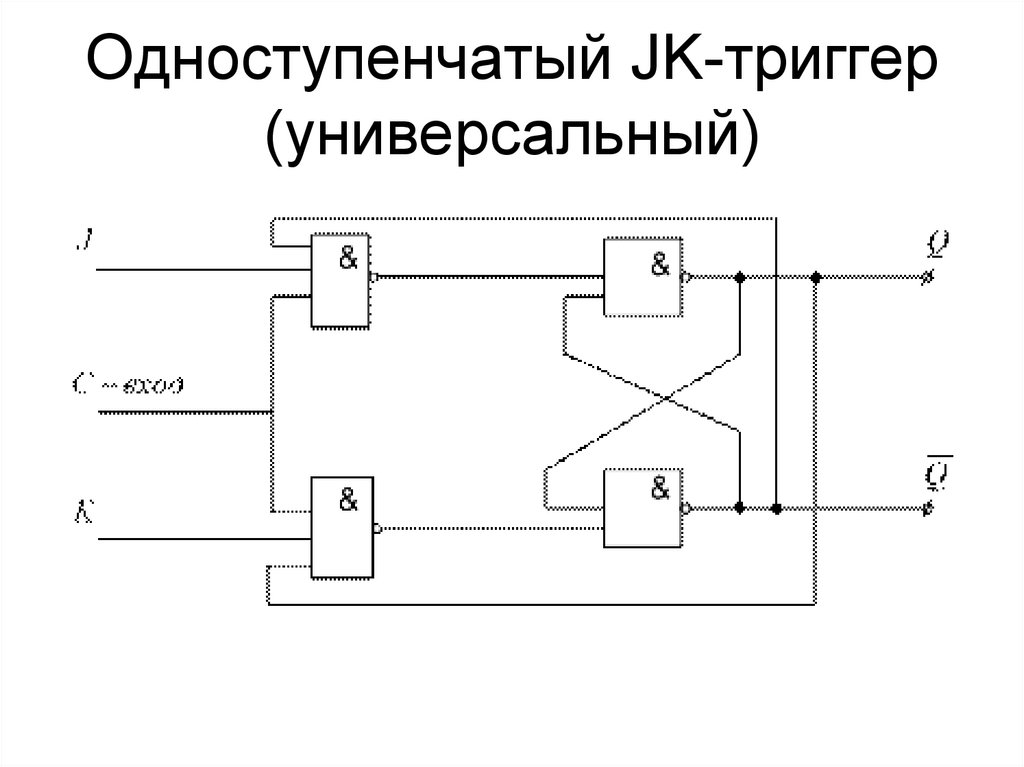

JK-триггеры.

JK-триггер –это триггер с двумя сигнальными и одним синхронным входами.

Такие триггеры часто называются универсальными, так как на их основе можно получить RS- и T-триггеры.

Название выводов у таких триггеров пошло от английских слов jerh -резкий толчок, kill — убить

Назначение- JK-триггеров универсальное.

Выполняется JK-триггер по двухступенчатой схеме с использованием основного и вспомогательного RS-триггера соединённых последовательно и имеющих обратную связь..

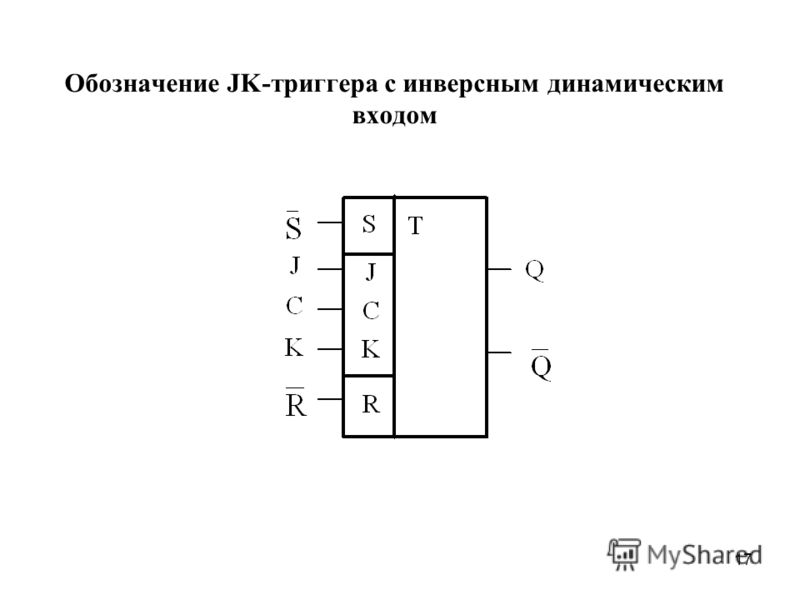

JK-триггеры получили следующее условное обозначение:

Рис. 0.26

Микросхемы JK-триггеров имеют обозначение ТВ. Например JK-триггер исполненный в комплекте микросхем 555 серии имеет обозначение — 555ТВ9.

Например JK-триггер исполненный в комплекте микросхем 555 серии имеет обозначение — 555ТВ9.

Информационные входы J и K аналогичны входам S и R тактируемого RSC- триггера.

Принцип действия JK-триггеров аналогичен RSC триггеру, но JK-триггеры не имеют запрещающей комбинации. Т.е. во время действия тактового импульса сигнал записывается в основной триггер, а в момент окончания сигнал считывается вспомогательным RS-триггером.

Схема JK-триггеров.

Рис. 0.27

На схеме, представленной выше, входы J, K являются информационными входами. Они аналогичны S и R входам тактируемого RSC-триггера (R эквивалентен K входу, S — J входу).

Работу (изменение состояний) JK — триггера при С=1 можно представить в виде следующей таблицы.

| Jn | Kn | Qn+1 |

| Qn | ||

При J=1, К=0 по срезу тактового импульса триггер устанавливается в единичное состояние, т. е. Q=1.

е. Q=1.

При J=0, К=1 — переключается в нулевое состояние, т.е. Q=0.

При J=0, К=0 — хранит раннее записанную информацию.

В данном триггере так же возможно осуществление счётного режима. Сказанное происходит при J=К=1. Триггер переключается каждым счетным импульсом приходящим на вход С..

Рассмотрим работу JK — триггера более подробно.

При J=K=0 на выходах DD1 и DD2 устанавливаются 1, которые для триггеров с инверсными входами являются пассивными сигналами. Следовательно, триггер Т1 и JK — триггер в целом своего состояния не изменяет.

Чтобы на выходе DD1 появился 0, необходимо чтобы J=1, C=1, =1. Тогда триггер Т1 переходит в 1 состояние, а по срезу тактового импульса и триггер Т2 переходит в 1. Следовательно, Q2=1.

При К=1, С=1, Q=1 на выходе DD2 появляется 0, переводящая триггер Т1 в нулевое состояние, а по срезу триггер Т2 в 0 и, следовательно, JK — триггер в целом переходит в нулевое состояние (Q=0, =1).

В отличие от RSC — триггеров одновременное присутствие единицы на сигнальных входах JK не является запрещающей комбинацией. При этом JK — триггер работает в счетном режиме, т.е. переключается спадом каждого тактирующего импульса.

На базе JК — триггеров можно построить любой из ранее рассмотренных.

Дата добавления: 2017-11-21; просмотров: 2176; ЗАКАЗАТЬ НАПИСАНИЕ РАБОТЫ

|

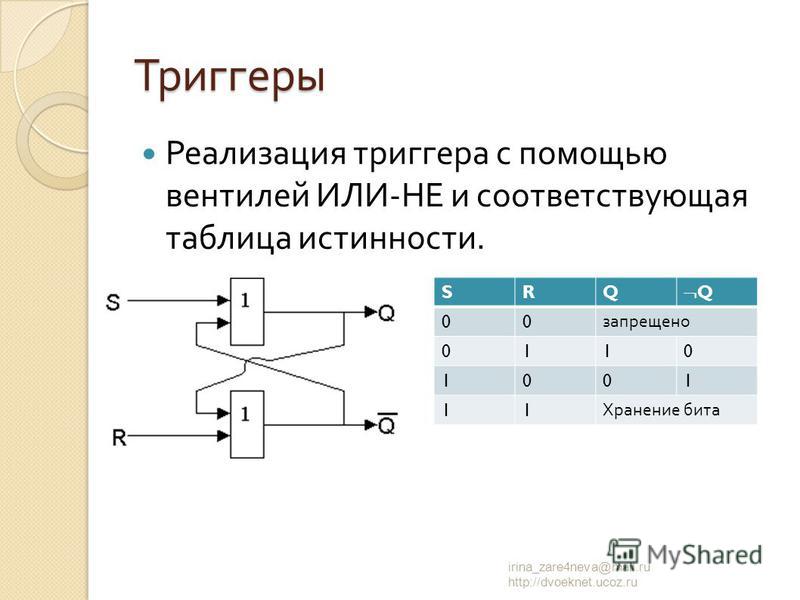

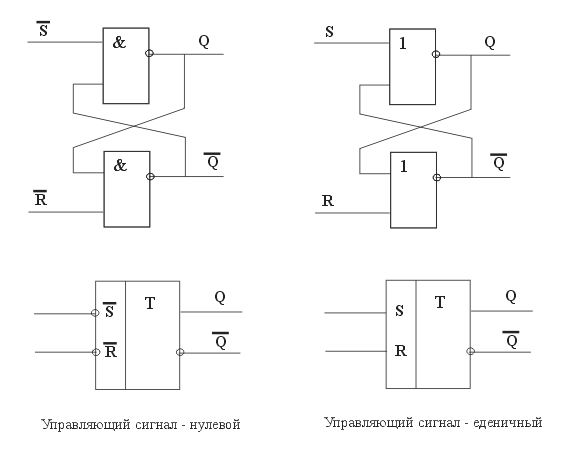

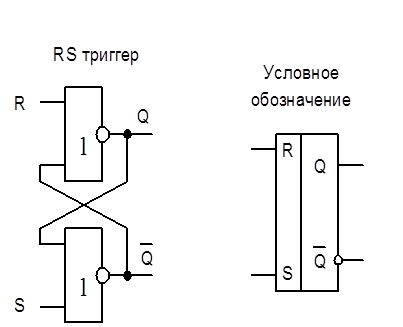

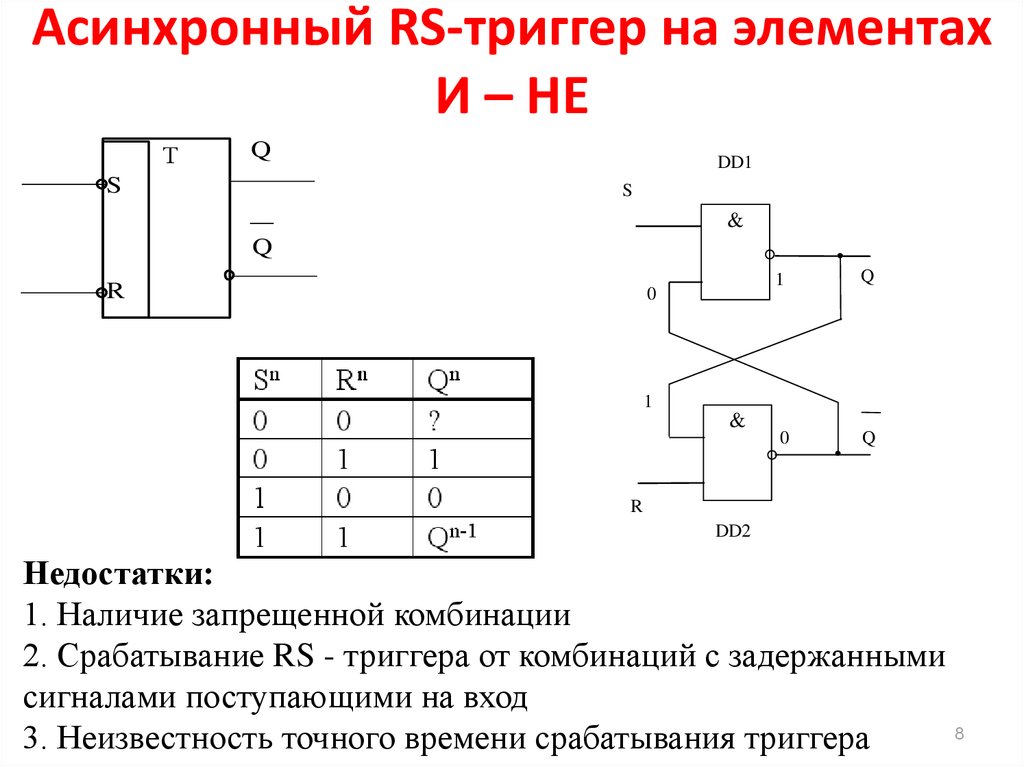

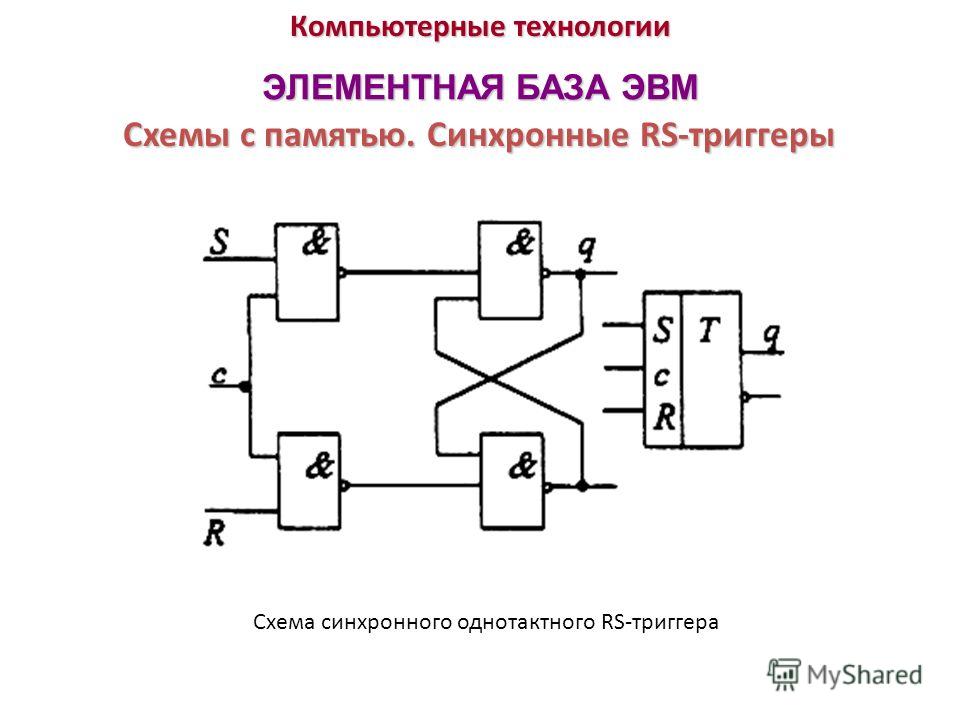

⇐ ПредыдущаяСтр 6 из 9Следующая ⇒ Триггером называют элементарный цифровой автомат, который имеет два устойчивых состояния. Одному из этих состояний присваивается значение 1, а другому — 0, Состояние триггера и значение хранимой двоичной информации определяются прямым и инверсным выходными сигналами. Если на прямом выходе Q имеется потенциал соответствующий логической 1, то триггер находится в единичном состоянии, если О-в нулевом состоянии. Потенциал на инверсном выходе противоположен главному выходу. Триггеры классифицируются по следующим признакам: 1. По способу записи информации различают асинхронные и синхронные триггеры. В асинхронных триггерах изменение состояния происходит при подаче сигналов на информационные входы. В синхронных (тактируемых) триггерах имеются кроме информационных входов один или несколько дополнительных для сигналов управления. Состояние таких триггеров изменяется при подаче синхронизирующих сигналов в соответствии со значением сигналов на информационных входах. 2. По способу управления информацией различают триггеры со статическим, динамическим, одноступенчатым и многоступенчатым управлением. При статическом управлении переключение триггеров вызывается уровнями сигналов, поступающих на информационные входы; при динамическом управлении — изменением уровней сигналов на информационных входах. Триггеры с одноступенчатым управлением имеют одну ступень управления, а с двухступенчатым — две ступени запоминания информации. Синхронные триггеры с одноступенчатым управлением называются однотактными. 3. По способу организации логических связей, определяющих особенности функционирования, различают RS,D,T,JK и другие типы триггеров. Основными параметрами триггеров являются: 1. Максимальная длительность входного сигнала; 2. Время задержки переключения триггера; 3. Разрешающее время триггера 30. Триггеры. Схема построения асинхронного RS-триггера на логических элементах Шеффера. Принцип работы, таблица переключения, временная диафрагма и УГО. Применение. 31. Триггеры. Схема построения синхронного однотактного RS-триггера на логических элементах. Принцип работы, таблица переключения, временная диафрагма и УГО. Применение. Синхронный однотактный RS-триггер. На входы логического элемента сигналы не всегда поступают одновременно, т.к. перед этим могут проходить через разное число узлов, не обладающих к тому же одинаковой задержкой. Это отрицательное явление можно устранить временным стробированием. когда на элемент кроме информационных сигналов подаются тактирующие (синхронизирующие) импульсы, к моменту прихода которых информационные сигналы успевают установиться на входах. Рис.62.Схема(а),УГО(б),таблица значений(в) и временные диаграммы (г) синхронного RS-триггера на логических элементах И-НЕ

Здесь элементы 1 и 2 образуют схемы входной логики синхронного управления RS- триггера. построенного на элементах 3 и 4.

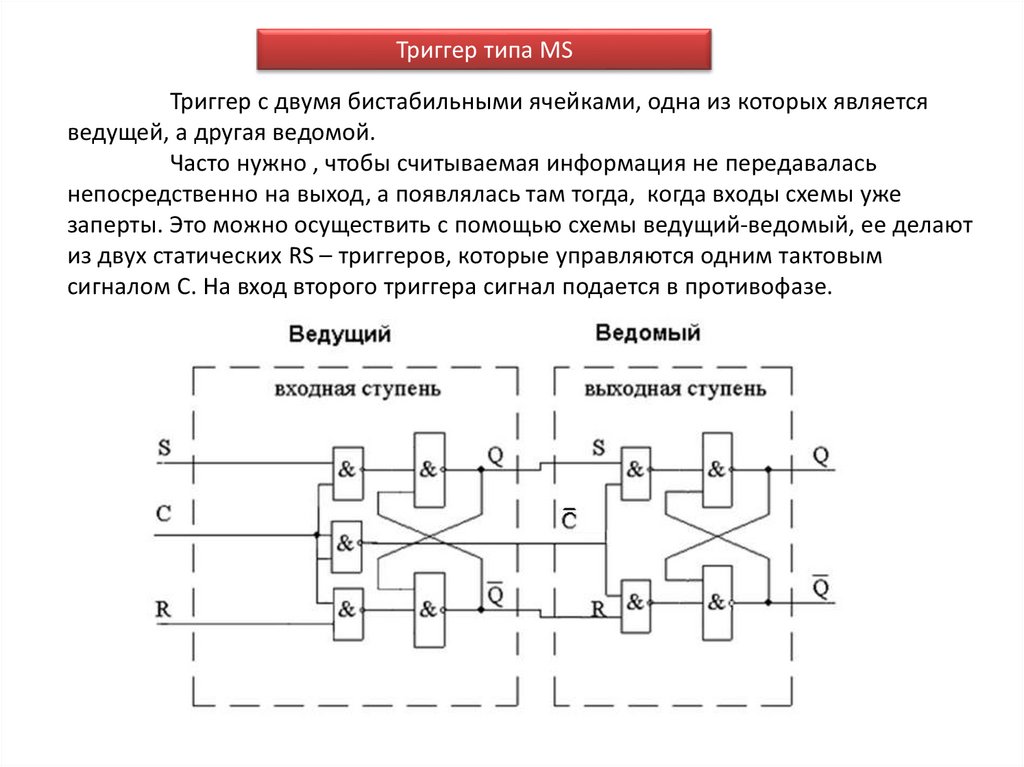

Поскольку входная информация поступает через дополнительные элементы 1 и 2, то она может быть записана в триггер только при поступлении на синхронизирующий вход тактирующего сигнала. 32. Триггеры. Схема построения синхронного двухтактного RS-триггера на логических элементах. Принцип работы, таблица переключения, временная диаграмма и УГО. Применение. Синхронный двухтактный RS -триггер. Устойчивая работа однотактных RS-триггеров в любой схеме возможно только при условии, что информация в триггер заносится после завершения передачи информации о прежнем его состоянии в другой триггер. Рис.63.Схема(а),таблица значений(б) и временные диаграммы(в) двухтактного синхронного RS-Триггера

Схема двухтактного синхронного RS-триггера состоит из двух однотактных RS- триггеров и инвертора в цепи синхронизации. Если на синхронизирующий вход триггера подаётся сигнал С=1, то входная информация, определяемая сигналами на R и S входах, заносится только в первый триггер. При этом второй триггер будет хранить предыдущюю информацию. Как только импульс синхронизации примет значение С=0, первый RS-триггер перейдёт в режим хранения, а с инвертора уровень С-инверсное равный «1” запишет информационное состояние первого RS-триггера во второй RS-триггер. Синхронный двухтактный триггер обычно имеет дополнительные асинхронные инверсные входы R и S, по которым он независимо от сигнала на синхронизирующем входе С переключается в состояние 0 или 1. Условное обозначение рассмотренного триггера имеет вид (рис.64). Рис.64.УГО двухтактного синхронного RS-триггера. Таким образом разница между однотактным и двухтактным синхронными RS- триггерами со статическим управлением состоит в следующем: однотактный синхронный RS-триггер можно переключить, если С=1 и при этом изменить комбинацию на установочных входах с прежней (например R=0, S=1) на новую (R=1, S=0) или наоборот; в двухтактном синхронном RS-триггере при С=1 вторая ступень отключена от первой, а при С=0 первая ступень не принимает информацию с входов R и S. Лишь при изменении сигнала на синхронизирующем входе С с 1 на 0 информация из первой ступени передаётся во вторую ступень и состояние выходов Q и Q-инверсное изменяется. 33. Триггеры. Схема построения. D-триггера со статическим управлением. Принцип работы, таблица переключения, временная диаграмма и УГО. Применение.34. Триггеры. Схема построения. D-триггеры Состояние в синхронных триггерах может изменится только во время действия синхроимпульса. В промежутке между синхроимпульсами выходные напряжения постоянны. Это позволяет создать на основе синхронизируемых RS-триггеров триггеры задержки — D-триггеры. D-триггер может быть одноступенчатым или двухступенчатым. Рис.68.Схема(а),УГО(б),таблица значений(в) и временные диаграммы(г) одноступенчатого синхронного D-триггера

1. Одноступенчатый D-триггер имеет вид (рис.68). При С=0 синхронный RS-триггер заблокирован уровнями логической 1 с выходов элементов И-НЕ. При С=1 уровень, поданный на информационный вход D, создаёт уровень логического 0 на входе S (D=1), либо на входе R (D=Q) асинхронного RS-триггера и триггер устанавливается в состояние, соответствующее логическому уровню на входе D. Как видно из временной диаграммы одноступенчатый D-триггер задерживает распространение входного сигнала на время паузы между сигналами. 2. Двухступенчатый синхронный D-триггер обеспечивает задержку входного сигнала на период (на один такт) следования синхронизирующих сигналов. Рис.69.Вариант построения(а),таблица значений(б) и временные диаграммы(в) двухступенчатого синхронного D-триггера.

Схема двухступенчатого синхронного D-триггера состоит из однотактного D-триггера и однотактного синхронного RS-триггера, тактируемых уровнем логической 1. и инвертора. При С=0 информация со входа D не принимается в триггер T-j. Этот уровень через инвертор подаётся на синхронизирующий вход триггера Т2 и состояние триггера Т1 передаётся Т2. При подаче на вход С уровня логической 1 на синхронизирующий вход триггера Т2 приходит логический 0 и связь между триггерами разрывается. Триггер Т1 при этом будет устанавливаться в состояние, соответствующее уровню на входе D. Триггеры с динамическим управлением.

При построении функциональных узлов вычислительных машин широко используются триггеры с динамическим синхронизирующим входом. Особенность таких триггеров состоит в том, что уровни с информационных входов воспринимаются триггером лишь в течение времени, когда на входе синхронизации С происходит переход с уровня логического 0 на 1, либо с логической 1 на 0.

Динамический RS-триггер Рис.73.Схема(а) и временные диаграммы(б) динамического RS-триггера. Пусть триггер хранит логическую 1 (Qn=1). Наличие на синхронизирующем входе триггера уровня С=0 независимо от комбинации входных сигналов на информационных входах будет блокировать состояние триггера, т.к. уровни логической 1 на выходах элементов И-НЕЗ и И-НЕ4 не смогут изменить состояние триггера Т5. Если перед подачей уровня логической 1 на вход С на информационных входах действовали уровни сигналов, например, Я-инверсное=0 и 8-инверсное=1, то при смене уровня на входе С с 0 на 1 на выходе элемента И-НЕ4 установится уровень логического 0, устанавливающий триггер Т5 в состояние 0 (Q=0). Одновременно уровень логического 0 с выхода элемента И-НЕ4 подаётся на выход элемента И-НЕ2 и на его выходе устанавливается уровень логической 1 независимо от последующих значений уровня сигнала на инверсном входе R. Уровень логического 0 с выхода элемента И-НЕЗ Аналогично упередаётся на вход И- НЕ1. устанавливая на его выходе уровень логической 1 независимо от последующих значений сигнала на инверсном входе S. Таким образом происходит логическое отключение триггера Т5 от входов. Изменение на входе С логического уровня с 1 на 0 заблокирует состояние триггера Т5. т.е. он будет хранить логический 0. Если на инверсных информационных входах будут действовать уровни сигнала S=0, R=1, то при смене уровня на входе С с логического 0 на 1 произойдёт переключение триггера Т5 из состояния 0 в состояние 1 (Qn=1). Рис.74.Условное графическое обозначение динамического RS-триггера. Динамически D-тригг ер.

Рис.75.Схема динамического D-триггера.

В триггерах с динамическим управлением по входу синхронизации, или просто динамических триггерах, запись входной информации происходит в момент перепада тактового сигнала. Запись может производится в момент положительного перепада тактового импульса (по фронту синхроимпульса) или в момент отрицательного перепада (по срезу синхроимпульса), Наиболее распространённым таким динамическим триггером является D-триггер, приведённый на рис.75. триггеров Т1 и Т2 и выходного триггера ТЗ. Рассмотрим основные режимы и особенности работы динамического О-тригтера; 1. Это нейтральная комбинация входных сигналов для выходного триггера ТЗ. При такой комбинации сигналов он находится в режиме хранения и выходные сигналы О-триггера не меняются. 2. Запись информации. До тех пор, пока С=0, один из двух триггеров Т1, Т2 находится в неопределённом состоянии.

X3=1 x2=1

X4=D̅ x1=x̅4̅=D

Какой из вспомогательных триггеров находится в устойчивом состоянии, а какой в неопределённом, зависит от уровня сигнала на входе D . Когда С=1, триггер, находившийся в устойчивом состоянии, сохраняет значение сигналов на своих выходах неизменным. Неопределённое состояние другого вспомогательного триггера при этом исчезает. В какое из двух устойчивых состояний он перейдёт, определяется значениями выходных сигналов триггера, находившегося в логически допустимом состоянии; из чего следует:

При D=0 x2=S̅ — остаётся в 1 X3=R̅ — переходит в 0 При D=1 x3=R̅ — остаётся в 1 X2=S̅ — переходит в 0

Сигнал принимающий нулевое значение, определяет состояние выходного триггера ТЗ. 3. Блокировка. Когда оба вспомогательных триггера Т1 и Т2 находятся в логически допустимых состояниях, они блокируют друг друга. При х3=0 заблокирован элемент 4. а при х2 =0 заблокированы элементы 1 и 3. 4. Подготовка к записи. Когда С=0 при установятся единичные уровни на выходах х2 и хЗ. и взаимная блокировка вспомогательных триггеров Т1 и Т2 снимается. Один из них перейдёт в неопределённое состояние, другой останется в устойчивом. Когда закончатся переходные процессы во вспомогательных триггерах Т1 и Т2, схема будет готова к записи информации в выходной триггер ТЗ. Условное обозначение О-триггеров с динамическим управлением имеет вид (рис.76). Рис.76.УГО динамических D-триггеров. 35. Триггеры. Схема построения асинхронного и синхронного Т-триггера. Принцип работы, таблица переключения, временная диаграмма и УГО. Триггер этого типа имеет только один информационный вход Т, называемый счётным входом, и изменяет своё состояние после прихода на счётный вход Т каждого управляющего (счётного) сигнала. Т-триггер реализует операцию сложения по mod 2, что и обусловило название триггера счётным триггером. Сигнал на его выходе Q появляется в два раза реже, чем на входе Т, т е. Т-триггер может использоваться как делитель частоты. 1. Асинхронный Т-триггер — может быть построен на базе двухтактного синхронного RS-триггера; выход Q соединяется с информационным входом R, инверсный выход — с информационным входом S. Информационным входом Т является синхронизирующий вход С.

Рис.65.Схема (а),таблица значений (б) и временные диаграммы (в) двухтактного асинхронного Т-триггера В этой схеме поступление сигнала Т=1 по входу С приводит к записи в двухтактный RS- триггер состояния, противоположного предыдущему. Сигнал на выходе триггера изменится только после завершения действия сигнала Т=1. В данной схеме единичный входной сигнал представляется спадом сигнала Т=1.

2. Синхронный Т-триггер — может быть построен на базе двухтактного RS-триггера с применением логических элементов И. Рис.66.Схема (а),таблица значений (б) и временные диаграммы (в) двухтактного синхронного Т-триггера

При Т=0 наличие синхронизирующего сигнала С=1 не сможет вызвать переключение Т-триггера, т.к. входы R и S двухступенчатого RS-триггера заблокированы уровнем логического 0 с выходов элементов 1 и 2. При наличии высокого уровня Т=1 каждый синхронизирующий сигнал на входе С=1 будет переключать триггер из одного состояния в другое, причём смена состояния происходит после окончания действия синхронизирующего сигнала на входе С (С=0). а электрических схемах Т-триггеры обозначается следующим образом (рис. Рис.67.УГО асинхронного(а) и синхронного(б) двухтактных Т-триггеров 36. Универсальный JK-триггер. Схема построения, принцип работы, таблица переключения, временная диаграмма и УГО. Особенности работы триггера. Применение. JK-триггер. Распространённым типом триггера в системах интегральных логических элементов является универсальный двухтактный JK-триггер. Триггеры этого типа отличаются от RS- триггеров тем, что при значениях входной информации, запрещённых для RS-триггеров, они инвертируют хранимую в них информацию. JK-триггер может быть построен на основе двухтактного синхронного RS-триггера.

Рис.71.Схема(а),таблица значений(б) и временные диаграммы(в) JK-триггера.

Входы J и К триггера (рис. 71) соответствуют входам S и R в RS-триггере, т.е. сигналы J=1, К=0 устанавливают триггер в состояние 1, а сигналы J=Q, К=1 — в состояние О независимо от предыдущего состояния. Однако в отличие от RS-триггера в JK-триггере сигналы логической 1 могут одновременно прийти на входы J и К. При J=1, К=1 и С=1 JK-триггер изменяет своё состояние на противоположное. Следовательно, при подаче на вход С серии синхронизирующих сигналов и J=K=1 JK-триггер работает в счётном режиме, т е. как Т- триггер.

У рассмотренного триггера имеются входы несинхронизируемой установки S̅ и R̅, с помощью которых при С=0 триггер может быть установлен в состояние 1 путём подами сигналов R̅=1 и S̅=0, либо в состояние 0 при подаче R̅=0 и S̅=1. Рис.72.Условное обозначение JK-триггера На базе синхронного JK-триггера можно реализовать синхронный и асинхронный Т- триггеры, D-триггер, синхронный RS-триггер.

⇐ Предыдущая123456789Следующая ⇒ |

Страница не найдена — Правовая защита огнестрельного оружия

Разговор с теми, кто не разбирается в оружии

6 октября 2022 г.

Разговор с теми, кто не разбирается в оружии Огнестрельное оружие может вызывать разногласия среди друзей, родственников и коллег. У некоторых благонамеренных людей есть серьезные опасения и отвращение — наряду с мнениями — по поводу оружия и его владельцев. Вот несколько советов и практических приемов, которые помогут владельцам оружия излагать свое мнение, развеять неправильные представления…

Подробнее

Что происходит во время уборки сцены?

30 сентября 2022 г.

Что происходит во время уборки сцены? Инциденты с самообороной иногда могут приводить к необходимости очистки места происшествия, чтобы удалить любые биологические опасности или другие вредные материалы с места, где произошел инцидент. Вы можете подумать, что полиция или офис коронера возьмутся за уборку места преступления, но…

Подробнее

Взлет и падение 40SW

26 сентября 2022 г.

Взлет и падение 40SW Созданный для того, чтобы предоставить ФБР боеприпас, способный конкурировать с возросшей огневой мощью преступников, патрон .40 Smith & Wesson имеет относительно короткую, но интересную историю. РОЖДЕНИЕ ТРАГЕДИИ ФБР В апреле 1986 года небольшая группа агентов ФБР напала на двух преступников…

Подробнее

Гидростатический удар: реальность или миф?

15 сентября 2022 г.

Гидростатический удар: реальность или миф? ЧТО ТАКОЕ ГИДРОСТАТИЧЕСКИЙ УДАР? Гидростатический удар — это принцип, при котором проникающий снаряд, такой как пуля, создает волну давления (похожую на звуковую волну в воздухе), что приводит к удаленному повреждению нервной системы, незначительному повреждению нервных тканей и, возможно, к быстрой недееспособности. воздействия на живые цели. Проще говоря, гидростатический удар — это…

Подробнее

Какое оружие соответствует требованиям Калифорнии?

12 сентября 2022 г.

Какое оружие соответствует требованиям Калифорнии? Чтобы убедиться, что вы соблюдаете законы Калифорнии об оружии, требуется некоторое обучение. По сравнению с остальной частью страны, в Калифорнии существует множество различных законов и процедур для владельцев огнестрельного оружия. Настолько, что многие, живущие за пределами штата, просто знают Калифорнию как «место, где…

Подробнее

Емкость журнала и закон

31 августа 2022 г.

Емкость магазина и закон В зависимости от того, в каком штате вы живете, то, что у вас есть огнестрельное оружие, не означает, что вы можете иметь магазин с нужным вам количеством патронов. Емкость магазина регулируется в некоторых штатах и постоянно является предметом потенциального законодательства о контроле над оружием. ИСТОРИЯ Самая ранняя история огнестрельного оружия…

Подробнее

Правовая защита огнестрельного оружия доступна в пяти новых штатах

24 августа 2022 г.

Правовая защита огнестрельного оружия доступна в пяти новых штатах (Аддисон, Техас) Правовая защита огнестрельного оружия, ведущий поставщик юридической защиты для самообороны, теперь будет предлагать полисы* в Арканзасе, Монтане, Неваде, Теннесси. и Висконсин с теми же преимуществами и ценами, что и членство* в большинстве других штатов. «Было интересно наблюдать за ростом правовой защиты огнестрельного оружия…

Подробнее

Стоит ли ломать ствол винтовки?

17 августа 2022 г.

Стоит ли разбивать ствол винтовки? Когда дело доходит до вопроса о том, следует ли «обкатывать» ствол новой винтовки, на самом деле есть только две точки зрения. 1. Да, конечно, должны. 2. Нет, конечно, не надо. И угадайте, что? Они оба правы. Просто…

Подробнее

Оружие, завещания и трасты

4 августа 2022 г.

Оружие, завещания и доверительные отношения Если у вас есть ружье или глушитель, естественно, они на 100% ваши. Следовательно, вы должны иметь право голоса в том, что с ними происходит и кто их получит после вашей смерти, верно? Так что главная цель должна состоять в том, чтобы правильно распределить управление и владение ими, чтобы ваши желания…

Следовательно, вы должны иметь право голоса в том, что с ними происходит и кто их получит после вашей смерти, верно? Так что главная цель должна состоять в том, чтобы правильно распределить управление и владение ими, чтобы ваши желания…

Подробнее

HR 1808 Ответ

30 июля 2022 г.

H.R. 1808 Ответ Палаты представителей H.R. 1808, также упоминаемый как «Запрет на штурмовое оружие от 2022 г.», оказывает прямое влияние на Вторую поправку и ее объем законно хранимого оружия. В случае успешного принятия законопроект заменит действующее законодательство штата и установит приоритет для штатов, в которых ранее не было законодательства. В результате принятия…

Подробнее

Harmony, 22-мм кнопка, головка аварийного останова, триггер и защелка

Основной контент начинается здесьSchneider Electric

MFR: Schneider Electric

MFR #: ZB4BT84

UPC: 7854369

Артикул #: 15393

Schneider Electric

MFR #: ZB4BT84

UPC: 7854369

Артикул #: 15393

Наличие

| Местоположение | В наличии Кол-во |

|---|---|

| РАЧИНСКИЙ РАСПРЕДЕЛИТЕЛЬНЫЙ ЦЕНТР | 10 |

| РАСПРЕДЕЛИТЕЛЬСКИЙ ЦЕНТР ДЕ-МОЙН | 0 |

$57,93 каждый

Описание

Harmony XB4, красная грибовидная кнопка аварийного останова, 40 мм, работает с защелкивающимся двухтактным механизмом. Эта головка кнопки аварийного останова/отключения легко комбинируется с контактными блоками и устанавливается в стандартные вырезы диаметром 22 мм и соединяется с помощью простых винтовых зажимных соединений. Он хорошо различим визуально на расстоянии благодаря четкому цвету и выступающей грибовидной форме 40 мм. Он ударопрочный, пыленепроницаемый, водостойкий и виброустойчивый благодаря степени защиты IP66/IP67/IP69./ IP69K. Он имеет металлическую рамку, что делает его идеальным для приложений, требующих высокой ударопрочности и виброустойчивости. Он предназначен для установки в стандартный вырез 22 мм, что обеспечивает совместимость при установке в ранее существовавшее оборудование. Широкий диапазон рабочих температур от -40°C до 70°C обеспечивает универсальность использования продукта.

Эта головка кнопки аварийного останова/отключения легко комбинируется с контактными блоками и устанавливается в стандартные вырезы диаметром 22 мм и соединяется с помощью простых винтовых зажимных соединений. Он хорошо различим визуально на расстоянии благодаря четкому цвету и выступающей грибовидной форме 40 мм. Он ударопрочный, пыленепроницаемый, водостойкий и виброустойчивый благодаря степени защиты IP66/IP67/IP69./ IP69K. Он имеет металлическую рамку, что делает его идеальным для приложений, требующих высокой ударопрочности и виброустойчивости. Он предназначен для установки в стандартный вырез 22 мм, что обеспечивает совместимость при установке в ранее существовавшее оборудование. Широкий диапазон рабочих температур от -40°C до 70°C обеспечивает универсальность использования продукта.

Технические характеристики

| Каталожный номер | ЗБ4БТ84 |

| Производитель | Шнайдер Электрик |

| Марка | Шнайдер Электрик |

| Суббренд | ЗБ4 |

| Описание гарантии | Договорная гарантия: 18 месяцев |

| Страна происхождения | Чехия |

| Сделано в США | № |

| Действие | ПОДДЕРЖИВАЕТСЯ — ТРИГГЕР ДЕЙСТВИЯ PUSH/PULL |

| Привод | спусковой крючок и механическая защелка; Красный гриб Ø 40 мм, без маркировки |

| Заявка | КРАСНЫЙ БЕЗ МАРКИРОВКИ |

| Корпус | NEMA 1/2/3/4/4X/13 |

| Индикатор | КРАСНЫЙ |

| Материал | Хромированный металл |

| Специальные возможности | БЕЗ ПОДСВЕТКИ |

| Стандарт | UL НОМЕР ФАЙЛА E164353 CCN NKCR — СЕРТИФИКАТ CSA НОМЕР ФАЙЛА LR44087 КЛАСС 321103 — МАРКИРОВКА CE |

| URL-адрес RoHS | https://checkaproduct. se.com/DistantRequestDispatcher.aspx?action=export&pid=657048&lang=en-us se.com/DistantRequestDispatcher.aspx?action=export&pid=657048&lang=en-us |

| УПК | 785 | 4369

| Тип изделия | Головка кнопки аварийного отключения |

| Размер | 0,87 |

| Условия окружающей среды | ИП 65 |

| Рабочая температура | -40-70 градусов Цельсия |

DiodesZetex 74LVC1G17W5-7 Неинвертирующий буфер с триггером Шмитта Push-Pull, 5-контактный SOT-25

Посмотреть все Буферы

3800 В наличии — БЕСПЛАТНАЯ доставка на следующий рабочий день доступна

Добавить в корзинуtickAdded

40

40 Просмотр в корзине40

Price Each (In a Pack of 100)

£0. 126

126

(exc. VAT)

£0.151

(inc. VAT)

Units Per unit Per Pack* 100 — 500 £0.126 £12.60 600 — 1400 £0.119 £11.90 1500 + £0.072 £7. 20

20 *price ориентировочный

Варианты упаковки:

checkmarkStandard Pack

empty-checkmarkProduction Pack

- RS Артикул:

- 822-8708 90778 Mfr

Деталь №:- 74LVC1G17W5-7

- Brand:

- DiodesZetex

Technical Reference

- docPdfSingle Schmitt-Trigger Buffer Datasheet

- docPdfDatasheet

- docPdfESD Control Selection Guide V1

Legislation and Compliance

Product Details

74LVC Family , Diodes Inc

Низковольтная КМОП-логика

Пакет с одним затвором

Рабочее напряжение: от 1,65 до 5,5 В

Совместимость: Вход LVTTL/TTL, Выход LVCMOS

74LVC Family

Specifications

Attribute Value Logic Family 74LVC Logic Function Buffer Number of Channels 1 Вход триггера Шмитта Да Тип входа Триггер Шмитта Output Type Push-Pull Polarity Non-Inverting Mounting Type Surface Mount Package Type SOT-25 Pin Count 5 Максимальный выходной ток высокого уровня -32 мА Максимальный выходной ток низкого уровня 32 мА Максимальное время задержки распространения при максимальной CL 14 ns @ 50 pF Maximum Operating Supply Voltage 5. Разное

Разное

126

126 20

20Пакет с одним затвором

Рабочее напряжение: от 1,65 до 5,5 В

Совместимость: Вход LVTTL/TTL, Выход LVCMOS

Разное

Разное

3.40. Двухтактный T-триггер

(слева) и его временные диаграммы

(справа)

3.40. Двухтактный T-триггер

(слева) и его временные диаграммы

(справа)

а с двухступенчатым — двухтактными.

а с двухступенчатым — двухтактными. Это явление называют состязаниями или гонками. В результате таких состязаний новые значения одних сигналов будут сочетатся с предыдущими значениями других сигналов, что может привести к ложному срабатыванию.

Это явление называют состязаниями или гонками. В результате таких состязаний новые значения одних сигналов будут сочетатся с предыдущими значениями других сигналов, что может привести к ложному срабатыванию. Т.о. синхронный триггер кроме входов R и S имеет вход синхронизации С. Закон функционирования данного триггера следующий: если на синхронизирующем входе действует уровень С=0, то триггер сохраняет своё состояние, т.е. триггер находится в режиме хранения, а если на синхронизирующем входе С=1, то триггер работает в режиме асинхронного RS-триггера. При отсутствии сигнала синхронизации триггер может быть установлен в состояние 0 или 1 подачей на дополнительные несинхронизирующие входы R-инверсное и S-инверсное сигналов, соответствующих логическому «О».

Т.о. синхронный триггер кроме входов R и S имеет вход синхронизации С. Закон функционирования данного триггера следующий: если на синхронизирующем входе действует уровень С=0, то триггер сохраняет своё состояние, т.е. триггер находится в режиме хранения, а если на синхронизирующем входе С=1, то триггер работает в режиме асинхронного RS-триггера. При отсутствии сигнала синхронизации триггер может быть установлен в состояние 0 или 1 подачей на дополнительные несинхронизирующие входы R-инверсное и S-инверсное сигналов, соответствующих логическому «О». Для этого приходится использовать две серии находящихся в противофазе синхроимпульсов. Подобный принцип обмена информацией реализован в двухтактных RS-триггерах.

Для этого приходится использовать две серии находящихся в противофазе синхроимпульсов. Подобный принцип обмена информацией реализован в двухтактных RS-триггерах.

D-триггера с динамическим управлением. Принцип работы, таблица переключения, временная диаграмма и УГО. Применение.

D-триггера с динамическим управлением. Принцип работы, таблица переключения, временная диаграмма и УГО. Применение.

После окончания действия сигнала на входе синхронизации (С=0) производится передача состояния триггера T-j триггеру Т2.

После окончания действия сигнала на входе синхронизации (С=0) производится передача состояния триггера T-j триггеру Т2.

После этого никакие последующие изменения уровней сигнала на входах не будут восприниматься триггером T5, пока на входе С не произойдёт перепад уровней сигнала с логического 0 на 1.

После этого никакие последующие изменения уровней сигнала на входах не будут восприниматься триггером T5, пока на входе С не произойдёт перепад уровней сигнала с логического 0 на 1. Режим хранения. Если С=0, то х2=S̅=1 и x3=R̅=1.

Режим хранения. Если С=0, то х2=S̅=1 и x3=R̅=1. Таким образом, выходной сигнал О-триггера Q принимает значение входных данных.

Таким образом, выходной сигнал О-триггера Q принимает значение входных данных. Применение.

Применение.

67).

67). Такие переключения возможны при сигнале на синхронизирующем входе С=1.

Такие переключения возможны при сигнале на синхронизирующем входе С=1.